# **SPC-180N**

# **TCSPC / FLIM Module**

## **High-Resolution Time-Correlated Single Photon Counting Module**

High-throughput PCI-Express interface

Ultra-fast, ultra-stable timing electronics

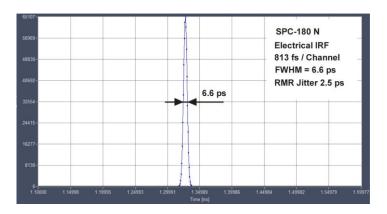

Electrical IRF width 6.6 ps FWHM

Internal timing jitter 2.5 ps RMS

Time-channel width down to 813 fs

Discriminator input bandwidth 4 GHz

Photon distribution and time/parameter-tag modes

Multi-detector / multi-wavelength capability

Excitation-wavelength multiplexing

Parallel operation of 2, 3 or 4 modules

Laser repetition rates up to 150 MHz

Dead time 80 ns

Saturated count rate 12.5 MHz

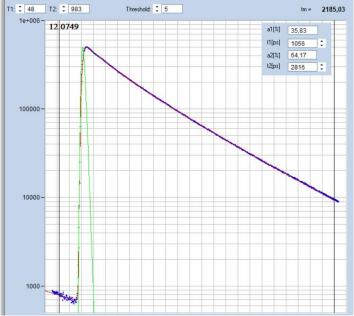

Fluorescence-decay experiments

Anti-bunching experiments

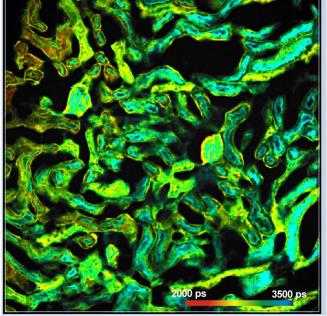

Single-wavelength FLIM, multi-wavelength FLIM

Fast-acquisition FLIM

Accumulated time-series FLIM

Simultaneous FLIM / PLIM

Mosaic FLIM

Metabolic imaging

Double-exponential FRET imaging

FLIM of fast physiological processes

Recording of Ca<sup>2+</sup> transients

fNIRS and NIRS experiments

Single-molecule spectroscopy

Fluorescence correlation

Becker & Hickl GmbH Nunsdorfer Ring 7-9 12277 Berlin, Germany Tel. +49 30 212 80 02-0 Fax. +49 30 212 80 02-13 email: info@becker-hickl.com https://www.becker-hickl.com

More than 28 years experience in TCSPC. More than 2500 TCSPC systems worldwide.

## **SPC-180N**

# **TCSPC / FLIM Module**

IRF stability

10 ps

over 50 seconds

0.5s per recording

#### **Photon Channel**

Principle

Discriminator Input Bandwidth

IRF Width, FWHM

RMS Timing Jitter

Variance in Time of IRF Centroid

Optimum Input Voltage Range

Min. Input Pulse Width

Threshold Zero Cross Adjust

#### **Synchronisation Channel**

Principle Discriminator Input Bandwidth Optimal Input Voltage Range Min. Input Pulse Width Threshold Frequency Range

Frequency Range SYNC Frequency Divider Zero Cross Adiust

### Time-to-Amplitude Converters / ADCs Principle

TAC Range

Biased Amplifier Gain

Biased Amplifier Offset

Time Range incl. Biased Amplifier

Min. Time / Channel

ADC Principle

Diff. Nonlinearity, Electrical

#### **Data Acquisition (Histogram Modes)**

Method

Dead Time

Saturated Count Rate

Useful Count Rate

Max. Counts / Time Channel (Counting Depth)

Overflow Control

Collection Time

Display Interval Time

Repeat Time

Sequential Recording

Synchronisation with Scanning

Routing

Count Enable

Experiment Trigger

#### Data Acquisition (FIFO / Parameter-Tag Mode)

Method

Online Display

FCS Calculation

Number of Counts of Decay / Waveform Recording

Dead Time

Saturated Count Rate, Peak

Sustained Count Rate (Bus-transfer Limited)

Max. Counts / Time Channel (Counting Depth)

Output Data Format (ADC / Macrotime / Routing)

On-board FIFO Buffer Capacity (Photons)

Macro Timer Resolution, Internal Clock

Macro Timer Resolution, Clock from SYNC Input

Routing

External Event Markers

Experiment Trigger

### Data Acquisition, FIFO Imaging

Synchronisation with Scanner

Detector / Wavelength Channels

Image Resolution, 64-bit SPCM Software

No of Time Channels

No. of Pixels, 1 Detector Channel

No. of Pixels, 16 Detector Channels

### Operation Environment

Online Display

Computer / Operating System Bus Connector Total Power Consumption Dimensions Constant Fraction Discriminator (CFD)

4 GHz

< 6.6 ps, FWHM

< 2.5 ps, RMS

<0.4 ps RMS over 100 seconds

-30 mV to -500 mV

200 ps

0 to -500 mV

-100 mV to +100 mV

Constant Fraction Discriminator (CFD)

4 GHz

-30 mV to -500 mV

200 ps

0 to -500 mV

0 to 150 MHz

1 - 2 - 4

-100 mV to +100 mV

Ramp Generator / Biased Amplifier 50 ns to 5 us 1 to 15 0 to 50 % of TAC Range 3.3 ns to 5 us 813 fs 50 ns Flash ADC with Error Correction < 0.5 % RMS, typ. <1 % peak-peak

on-board multi-dimensional hardware histogramming process 80 ns, independent of computer speed

12 MHz 6 MHz 2<sup>16</sup>-1 none / stop / repeat and correct

0.1 us to 100,000 s 10 ms to 100,000 s 0.1 us to 100,000 s Unlimited recording by memory swapping

pixel, line and frame clocks from scanning device 7 bit TTL 1 bit TTL TTL

Parameter-tagging of individual photons and continuous writing to disk Decay function, FLIM, FCS, Cross-FCS, PCH, MCS traces Multi-tau algorithm, online calculation and online fit

unlimited 80 ns 12 MHz 5 MHz unlimited 12 / 12 / 4 bit 2·10<sup>6</sup>

25 ns, 12 bit, overflows marked by MTOF entry in data stream 10 ns to 100 ns, 12 bit, overflows marked by MTOF entry in data stream

4 bit TTL 4 bit, TTL TTL SPC-180 N

IR Stability

recorded over 50 sec

Buildup of images from time- and wavelength tagged data up to 8 images in different time and wavelength windows or from different modules via Frame Clock, Line Clock, and Pixel Clock pulses

1 to 16

64 256 1024 4096 4096 x 4096 2048 x 2048 1024 x 1024 512 x 512 1024 x 1024 512 x 512 256 x 256 128 x 128

PC Pentium, multi-core, >8GB RAM, Windows 10, Windows 11

PCI-ex

approx. 12 W from +12V

230 mm x 130 mm x 18 mm

#### Related Products

SPC-180NX, SPC-180NXX TCSPC Modules, SPC-150N, SPC-150NX, SPC-150NXX TCSPC modules HPM-100 GaAsP and GaAs hybrid detectors, DCC-100PCle detector controller BDL-SMN ps diode lasers, BDS-SM, -SMY, -MM picosecond diode lasers, SPCImage NG data analysis software

#### Related Literature

W. Becker, The bh TCSPC Handbook, 9th edition (2021). 950 pages, available on https://www.becker-hickl.com. Please contact bh for printed copies. The bh TCSPC Technique, Principles and Applications. Overview brochure, 27 pages. Available on https://www.becker-hickl.com

### **International Sales Representatives**

US: Boston Electronics Corp tcspc@boselec.com www.boselec.com

UK: Photonic Solutions PLC sales@psplc.com www.psplc.com

Japan: **Tokyo Instruments Inc.** sales@tokyoinst.co.jp www.tokyoinst.co.jp

China: **DynaSense Photonics Co. Ltd.** info@dyna-sense.com www.dyna-sense.com